數字邏輯:

第一部分 邏輯代數

自己手寫一個重點思維導圖,字比較丑,湊合看一下吧

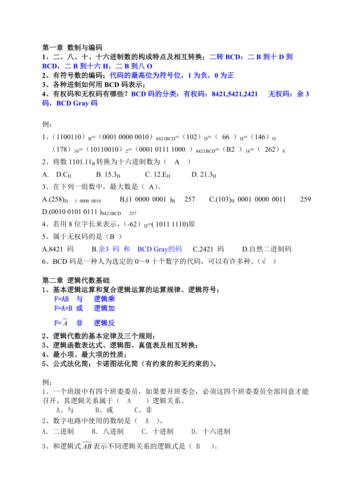

一.進制轉換

原碼 反碼 補碼 8421BCD 碼 格雷碼

可以通過書 P15 頁的第一章習題進行練習鞏固

二.門 (書 P19 邏輯門:國際常用符號 曾用符號 國家標準符號) 與運算或運算非運算與非邏輯(先求與,再求非)或非邏輯(先求或,再求非)與或非邏輯(先求與,再求或,再求非)異或邏輯

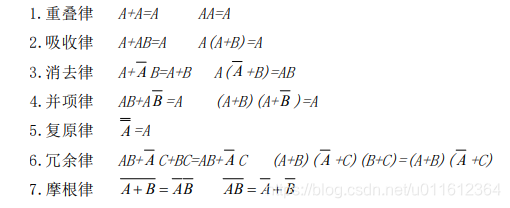

(1)奇數個變量的異或=同或 偶數個變量的異或=同或非同或邏輯 三.基本運算定律

四.反函數 反演規則 對偶函數 對偶規則 反演規則(求反函數)

·變 + + 變· 0 變 1 1 變 0 原變量變為反變量 反變量變為原變量對偶規則(求對偶函數) 用于證明函數是否相等

·變 + + 變· 0 變 1 1 變 0 ·變 + +變· 同樣適用于異或 變同或 五.最小項 最大項

最小項之和

標準的與或表達式:每一個與項包含了所有輸入變量

(原變量記為 1,反變量記為 0)

表示:n 變量的最小項的個數:0~ 2^n-1

性質:

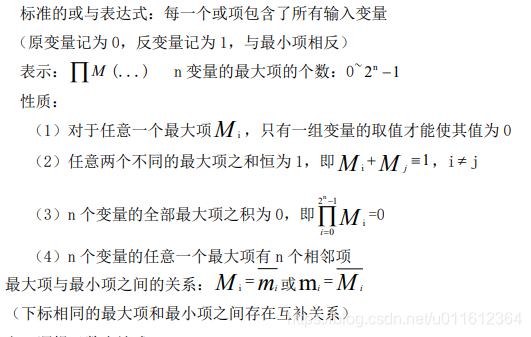

最大項之積

標準的或與表達式:每一個或項包含了所有輸入變量

(原變量記為 0,反變量記為 1,與最小項相反)

表示: n 變量的最大項的個數:0~ 2^n-1

性質:

六.邏輯函數表達式 將函數展開成“積之和”,“最簡與或表達式”的形式將函數展開成“和之積”,“最簡或與表達式”的形式

方法:公式法卡諾圖(順序:00 01 11 10)

注意:通過卡諾圖化簡時:

1)先圈只有一種情況的“1”,并且要圈的面積最大(1,2,4,8,16)【沒有 6】

2)畫一個圈就拉出一個線寫出與式(或式)

3)畫完后檢查,是否存在一個圈,里面所有的元素都被其他圈所圈過了,如果是,則要去掉(嚴格按照第一步驟不會出現這一步)

4)不能通過最簡或與表達式轉換成最簡與或表達式

5)在卡諾圖中“1”的位置很多且很復雜的時候,可以考慮圈“0”,但是要注意圈“0”的時候,使用的是負邏輯

6)卡諾圖中,無關項的位置打“×”或者“d”,在畫圈的時候,站在“1”或者“0”的角度上畫圈,將無關項也考慮進去

7)如果是通過真值表化簡,將真值表輸出為 1 的那幾行所對應的填入卡諾圖進行化簡 第二部分組合邏輯電路的分析與設計

簡單概述

組合邏輯電路的基本特點:①結構上無反饋,②功能上無記憶,③電路在任何時刻的輸出都由該時刻的輸入信號完全確定,與過去的輸入和過去的狀態無關。

一、組合邏輯電路的分析

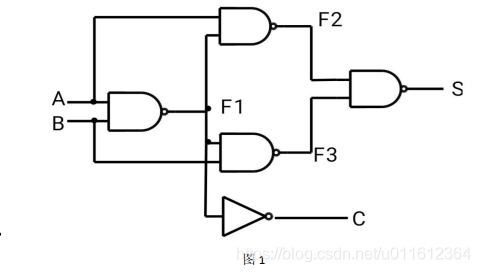

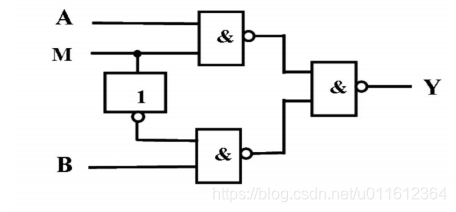

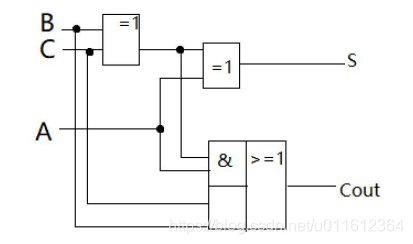

舉栗:分析下圖電路的功能

分析步驟:

(1)由邏輯電路圖逐級寫出邏輯表達式

(2)由邏輯表達式化簡為最簡與或表達式

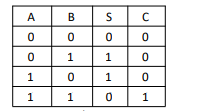

(3)畫真值表

(4)分析電路的功能

已知 A,B 為輸入變量,S,C 為輸出變量,由真值表的前三行可知,S 是在做 A,B

的加法,C 始終為 0,看到第四行的時候,A,B 的輸入均為 1,如果按照之前的猜

測,S 是對 A,B 做加法,此時 S 用二進制表示應該是 10,但 S 的值為 0,此時 C

為 1,不難想到 C 是用來表示進位位的,因此該電路的功能為一個二進制的加法

器,A 為被加數,B 為加數,S 為兩者之和,而 C 為進位位,但因該加法器未考

慮低位向高位的進位,故該加法器是一個半加器。

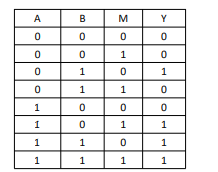

按照上述步驟:

(1)由邏輯電路圖逐級寫出邏輯表達式

(2)將邏輯表達式化簡為最簡與或表達式

(3)畫真值表

(4)分析電路功能

觀察真值表可知,當 M=1 時,Y=A;當 M=0 時,Y=B;因此,該電路是一個二選一

的電路。

二、組合邏輯電路的設計

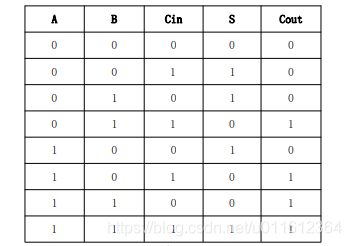

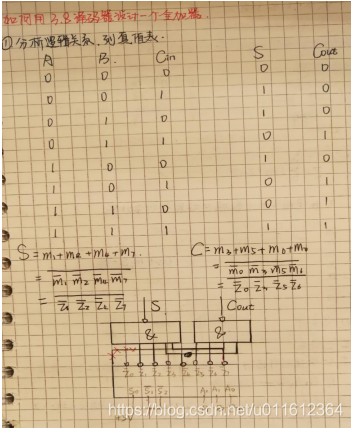

舉栗:1、設計一個全加器

步驟:

(1)分析事件的因果關系,確定輸入變量和輸出變量

全加器有三個輸入變量,定義為 A,B,Cin,有兩個輸出變量,定義為 S 和 Cout。

(2)定義邏輯狀態的含義,并對變量賦值

當 A=1 時,表示此時輸入的 A 的值為 1,當 A=0 時,表示此時輸入的 A 的值為 0,

B,Cin 同理;

當 Cout=1 時,表示 A,B,Cin 之和產生了進位位,Cout=0 時,表示 A,B,Cin 之和

未產生進位位;

當 S=1 時,表示 A,B,Cin 中其中任意一個變量取值為 1,另外兩個變量取值為 0,;

或者 A,B,Cin 均為 1;當 S=0 時,表示 A,B,Cin 中其中任意兩個變量取值為 1,

另一個變量取值為 0。

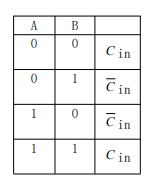

(3)根據給定的因果關系列出真值表

(4)由真值表寫出對應的邏輯函數表達式

(5)由邏輯函數表達式畫出邏輯電路圖

三、編碼器和譯碼器

1、編碼器:將十進制轉化為二進制

輸入值的有效性:①原變量輸入=正邏輯輸入=高電頻輸入=某輸入引腳=1

②反變量輸入=負邏輯輸入=低電頻輸入=某輸入引腳=0

還有部分優先編碼器介紹,詳情 P86。

2、譯碼器(是編碼器的逆過程,是將二進制轉化為十進制)

以 38 譯碼器為栗:38 譯碼器有三個使能端 1 S , 2 S , 3 S (一高兩低),三個地址

選 擇 端 A0 , A1 , A2 ( 分 別 接 外 部 的 三 個 輸 入 變 量 ) , 八 個 輸 出 端

Zi (i=0,1,2······7),其中,每一個 Zi ? mi (mi 是由 A0A1A2 三變量構成),

如當Z0 =0 有效時,Z0 ? A0 A1 A2 , A0A1A2 =000。

如何用 38 譯碼器來設計一個全加器呢?

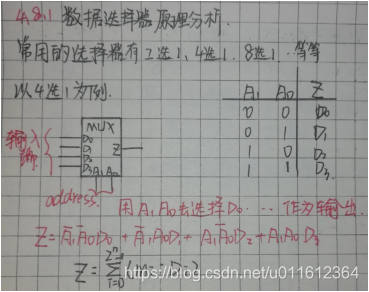

四、數據選擇器

功能:從多輸入中選擇一個數據作為輸出。

常見的數據選擇器有 2 選 1,4 選 1,8 選 1,16 選 1,以 4 選 1 為例,A1A0 為地址

選擇端, 是輸入端,Z 是輸出端,這里的選擇的意思是用 A1A0 去選擇

作為輸出。

重點:如何用數據選擇器去設計一個具有完善功能的電路呢?

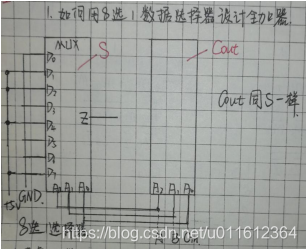

舉個栗子:如何用 8 選 1 數據選擇器設計一個全加器?

分析:全加器有三個輸入變量,兩個輸出變量;可以將三個輸入變量 ABCin 與 8

選 1 數據選擇器的三個數據輸入端 A0A1A2 對應連接,所以很容易解決輸入變量;

But。。。怎么表示全加器的輸出變量 S 和 Cout 呢,因為 8 選 1 數據選擇器只有

一個輸出端,所以,此時,一個 8 選 1 還不夠,需要用到兩個 8 選 1 的數據選擇

器。

全加器: S=m1+ m2+ m4+ m7

Cout = m3 + m5 + m6 + m7

步驟:

(1)考慮讓數據選擇器的三個地址輸入端與全加器的三輸入變量一一對應

(2)用展開式與全加器的兩個式子相對應。兩個 8 選 1 的 A2A1A0 必須與 ABC 一一對應.

3)兩個把 8 選 1 的兩個輸出分別是 S 和C out

如何用 4 選 1 數據選擇器設計全加器?

分析:4 選 1 的數據選擇器跟 8 選 1 數據選擇器相似,都會用到兩個數據選擇器,

但是,它更難一些,難就難在,4 選 1 的數據選擇器只有兩個地址輸入端,而全

加器有三個輸入變量,那么,怎么用4選1的數據選擇器去表示第三個輸入變量?

全加器: S=m1+ m2+ m4+ m7

Cout = m3 + m5 + m6 + m7

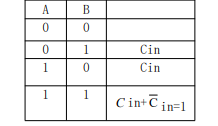

當計算 S 時,將 AB=00,01,10,11 時分別代入上面的式子,可得下表。

當計算 Cout 時,將 AB=00,01,10,11 時分別代入上面的式子,可得下表。

由上述可知,故 Cin 與 D1 D2連接, D0 接地, D3 接 Vcc 或+5V。

由此,可得電路圖為:

第三部分 時序電路分析與設計 第五章:觸發器

前言:

觸發器本身是由多個邏輯門構成的,與組合邏輯電路不同的是,觸發器內部存在輸出對輸入

信號的反饋,因而觸發器具有記憶輸入信息的功能。

5.1.1 觸發器的電路結構和特點

書上 115 頁

一些補充:

觸發器是雙穩態電路

雙穩態電路:

在電子電路中,其雙穩態電路的特點是:在沒有外來觸發信號的作用下,電路始終處于原來

的穩定狀態。在外加輸入觸發信號作用下,雙穩態電路從一個穩定狀態翻轉到另一個穩定狀

態。由于它具有兩個穩定狀態,故稱為雙穩態電路。

我的理解:

它有兩個穩定的狀態:0 狀態(Q=0,Q 非=1)和 1 狀態(Q=1,Q 非=0)

在不同的輸入情況下,它可以被置成 0 狀態或者 1 狀態

當輸入信號消失后,所置成的狀態能夠保持觸發器的定時(時鐘)端 CP

這個 CP 端的作用就是觸發我們的觸發器。為什么有些觸發器需要 CP 端呢?

解釋:

書上 119 頁 5.2.3

沒有 CP 端的觸發器,輸入信號直接加到輸出門的輸入端

CP 端有個小圓圈,代表 CP 端要為下降沿時,觸發器才工作,輸入信號才被接受

CP 端沒有辣個小圓圈,代表 CP 端要為上升沿時,觸發器才工作,輸入信號才被接受

鐘控 RS 觸發器必須要 CP=1 時,觸發器才工作。(書上 120 頁)

5.1.2 觸發器的邏輯功能和分類

根據電路結構分類:

基本 RS 觸發器,鐘控 RS 觸發器,同步觸發器,主從觸發器,邊沿觸發器

根據電路邏輯功能分類:

RS 觸發器,D 觸發器,JK 觸發器,T 觸發器,T’觸發器

基本觸發器和鐘控觸發器的定義:

書上 116 上面一點

5.2 基本 RS 觸發器

電路圖:書上 116

輸入:R 非,S 非

輸出:Q,Q 非

特性方程和約束條件非常重要!

為什么有這個約束條件?

書上 116 頁下面(4)

RS 觸發器總結:

3. 無論是哪種 RS,特性方程都一樣

4. 與非門的約束條件和或非門的在數學上等價,但是在電路中不等價

鐘控 RS 的約束條件在基本 RS 上加了個 CP=1 的約束

主從 RS 的約束條件在基本 RS 上加了個 CP 為下降沿的約束

5. R 端習慣上叫做復位端,Reset.該端有效時,會把狀態 1 置為狀態 0

6. S 端習慣上叫做復位端,Set.該端有效時,會把狀態 0 置為狀態 1

5.3 D 觸發器

重點掌握特性方程

5.4JK 觸發器

重點掌握特性方程

注:當 J=1,K=1 時,Q(n+1)=Qn 非,這就變成了 T’觸發器了。

5.5 其他觸發器

T 觸發器,T’觸發器 把特性方程記到就差不多了

5.7 觸發器的相互轉換

書上 129 頁 重要

5.8 觸發器的應用

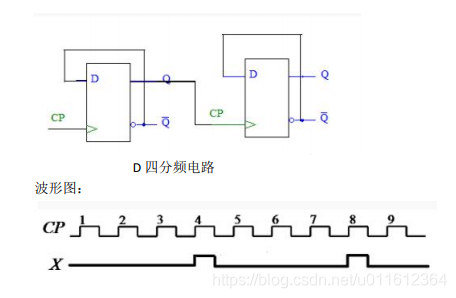

分頻器:書上 132 頁

書上的例題是二分頻,倘若想要 4 分頻,就得要 2 個觸發器,以此類推。

還有書上用的是邊沿 D 觸發器,但是我們也可以用 JK 觸發器來實現,只要滿足 J=1,K=1.

第六章

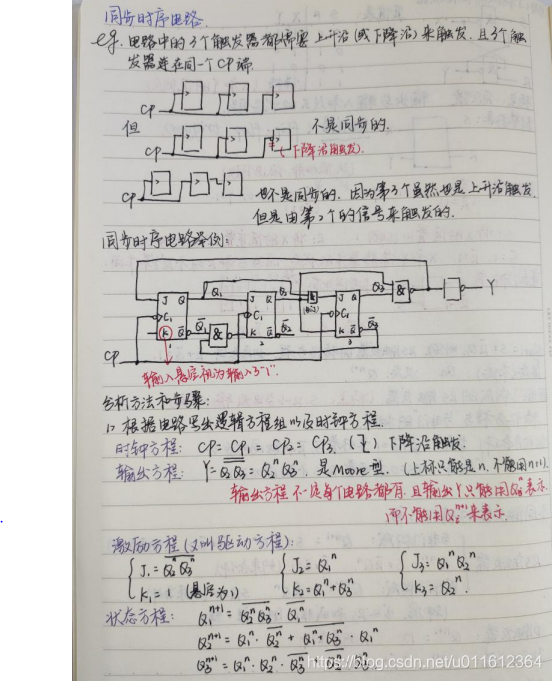

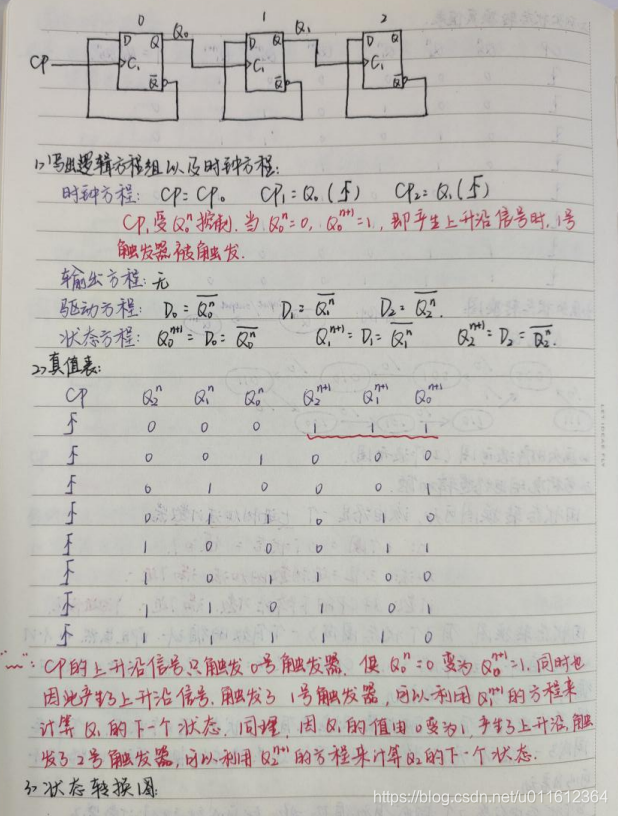

6.1 時序電路的分析步驟

書上 141 頁

7. 電路圖,觀察是同步時序電路還是異步時序電路,觀察觸發器類型,JK 還是 D 等。

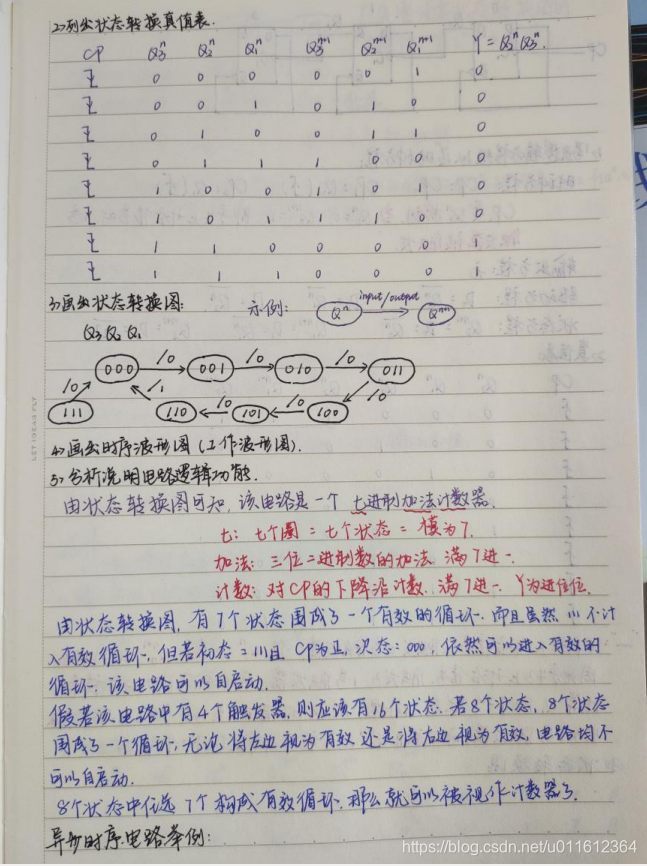

8. 寫出時鐘方程,驅動方程(激勵方程),輸出方程和狀態方程

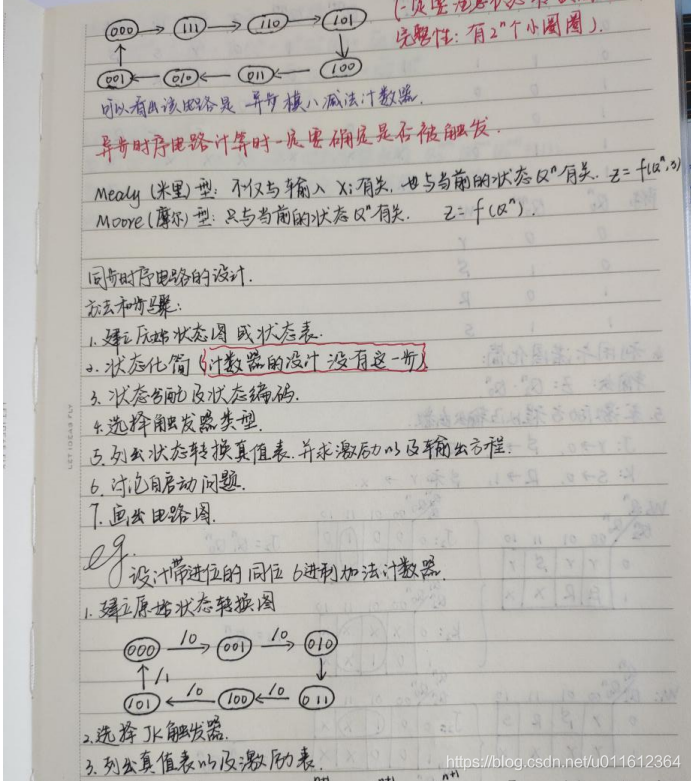

9. 列真值表

10. 畫狀態轉換圖

11. 判斷電路的邏輯功能

有效循環,自啟動的一些概念 書上 143 中間

注意點:

12. 同步時序電路的時鐘方程是形如 CP=CP0=CP1=CP2. 2. 列真值表時 CP 要列出來

13. 邏輯功能有時候可能一眼看不出來,可以試試交換一下 Q1,Q2,Q3 的順序。

6.2 時序電路的設計步驟

1.建立原始狀態圖

2.狀態化簡

3.狀態分配及狀態編碼

4.選擇觸發器類型

5.列出真值表

6.討論自啟動問題

7.畫出電路圖

*請認真填寫需求信息,我們會在24小時內與您取得聯系。